Content

- Rah-Veer: Save a Life Without Fear

- Design Linked Incentive Scheme

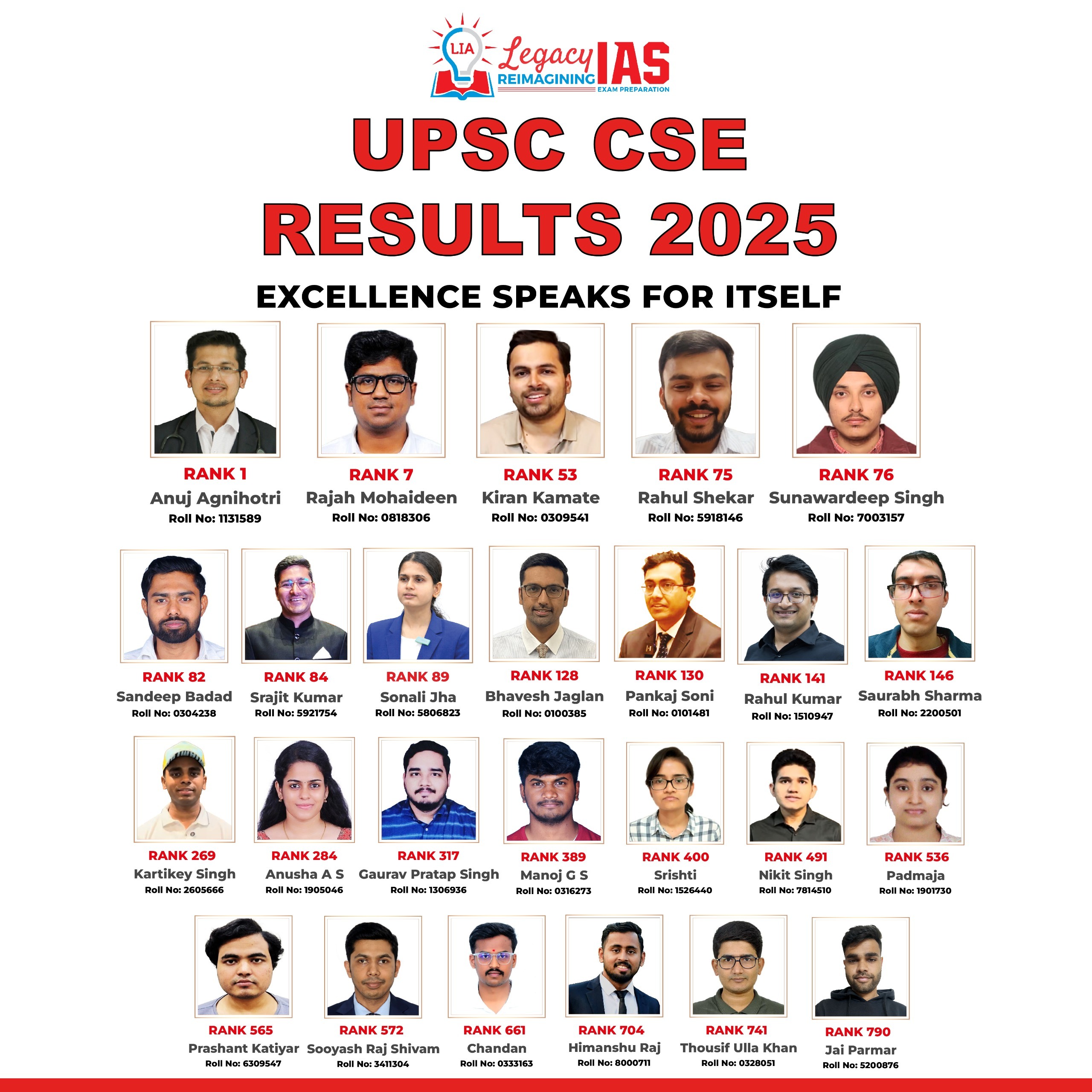

Rah-Veer: Save a Life Without Fear

Why in News ?

- The Ministry of Road Transport & Highways (MoRTH) is highlighting the Rah-Veer (Good Samaritan) protections and reward scheme, reinforcing public awareness that bystanders helping road-accident victims are legally protected .

- Linked to India’s broader road-safety strategy under the Motor Vehicles (Amendment) Act, 2019 and the Good Samaritan Rules, 2020.

Relevance

- GS-II (Health): Golden Hour emergency-care governance; cuts preventable deaths and disability.

- GS-III (Public Safety / Disaster Management): Community-led first response; Safe-Systems / Vision Zero approach.

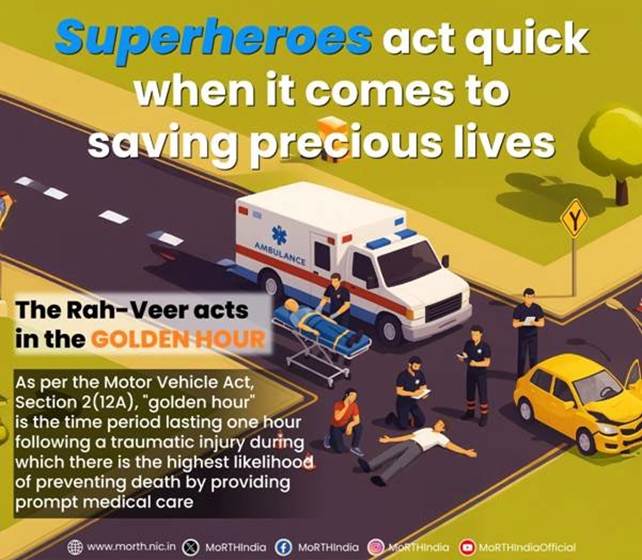

Basics — Concept & Rationale

- Golden Hour: First hour after a serious injury when timely medical care can prevent death or disability.

- Problem Addressed: Bystanders often hesitate to help due to fear of police, court procedures, hospital liabilities, or payment demands.

- Policy Logic: Encourage lifesaving intervention by removing legal, procedural, and financial risks for helpers.

Legal Architecture

- Statutory Basis: Section 134A, Motor Vehicles (Amendment) Act, 2019.

- Operational Rules: Good Samaritan (Protection from Civil and Criminal Liability) Rules, 2020.

- Judicial Foundation: Supreme Court directions in SaveLIFE Foundation v. Union of India (2016) — made Good Samaritan guidelines binding nationwide.

Good Samaritan — Rights & Protections

- No civil or criminal liability when acting in good faith.

- Right to anonymity — no mandatory disclosure of name/address.

- No detention or harassment by police or hospital authorities.

- If volunteering as witness — statement can be recorded only once, at a convenient time/place (including video-conference).

- Hospital acknowledgement must be issued on request.

- No obligation to stay back after admission of the victim.

- No payment liability — hospitals cannot demand treatment costs from the helper.

- No compulsion to file FIR or give evidence unless the person voluntarily agrees.

Obligations on Authorities / Institutions

- Hospitals (public & private) must:

- Provide immediate emergency care without pre-payment.

- Issue simple acknowledgement to the Good Samaritan.

- Not detain the helper for procedural formalities.

- Police must:

- Avoid unnecessary questioning or repeated summons.

- Treat Good Samaritans with dignity and privacy safeguards.

- State Governments / MoRTH:

- Conduct awareness programmes and institutional compliance audits.

Rah-Veer Reward & Recognition Scheme

- ₹25,000 reward + Certificate of Appreciation for helping a crash victim reach medical care within the Golden Hour.

- Eligibility up to five recognitions per person per year (repeat acts of assistance).

- Objective: build a culture of empathy, courage, and community responsibility on roads.

Data & Context

- India records one of the highest global road-crash fatalities.

- Economic loss from road accidents estimated at ~3% of GDP (as noted in studies cited by MoRTH / IIT-Delhi).

- A significant share of preventable deaths occurs due to delays in first response during the Golden Hour — bystander hesitation is a major factor.

Impact Pathways — Why the Policy Matters ?

- Reduces Golden-Hour mortality by encouraging early evacuation.

- Builds trust between citizens, hospitals, and law-enforcement.

- Shifts policy focus from punitive perception to public-spirited participation.

- Supports Vision Zero / Safe-Systems approach in road safety.

Implementation Gaps & Challenges

- Low public awareness → fear still persists in many regions.

- Variable compliance by private hospitals & local police.

- Lack of standardised claim processing for rewards in some states.

- Need for training of frontline officials and routine audits.

Way Forward

- Nationwide awareness campaigns in schools, highways, transport hubs.

- Emergency responder training for citizens (basic first-aid modules).

- Digital reward & acknowledgement portal for transparency.

- Integration with 112 emergency response and ambulance networks.

- Periodic compliance monitoring & penalties for violations by institutions.

Prelims Pointers

- Section under MV Act: 134A.

- Rules notified: 2020.

- Liability status: Protected from civil & criminal liability when acting in good faith.

- Supreme Court basis: SaveLIFE Foundation case (2016).

- Reward under Rah-Veer scheme: ₹25,000 + certificate.

Design Linked Incentive Scheme

Why in News ?

- The Government of India highlighted progress under MeitY’s Design Linked Incentive (DLI) Scheme — a pillar of the Semicon India Programme — aimed at building a self-reliant fabless semiconductor design ecosystem.

- The update reports rapid scaling of DLI-supported chip-design projects, talent creation, patents, tape-outs, and private-investment leverage.

Relevance

- GS-III (S&T & Indigenisation): Strategic chip-design capability, IP ownership, RISC-V/SoC innovation; design-to-deployment ecosystem.

- GS-III (Economy & MSMEs): Startup/MSME up-gradation, investment leverage, and high-value manufacturing linkages (design ≈ major share of value addition).

Basics — Semiconductor Value Chain & Policy Logic

- Chip design = main value creator

- Contributes up to 50% of value addition

- Accounts for 20–50% of BOM cost

- Drives 30–35% of global semiconductor sales via the fabless segment

- Fabless model = high-value, low-capex

- Value lies in design + IP, not fabrication alone.

- Strategic rationale for India

- Reduce import dependence on core technologies

- Retain IP ownership

- Attract downstream manufacturing & assembly

- Strengthen technology sovereignty & resilience

Scheme Architecture — Core Facts

- Implementing Ministry: MeitY

- Nodal Agency: C-DAC under the India Semiconductor Mission (ISM)

- Umbrella Programme: Semicon India Programme (₹76,000 crore outlay)

- Coverage: ICs, chipsets, SoCs, systems, IP cores, semiconductor-linked designs

- Lifecycle support: Design → prototyping → validation → deployment

Eligibility

- Startups & MSMEs → incentives + design-infrastructure support

- Other domestic companies → deployment-linked financial incentives

- Definitions aligned to:

- MSME notification (1 June 2020)

- DPIIT Startup notification (19 Feb 2019)

- FDI Policy, 2017 (domestic ownership norms)

Financial Incentives

- Product Design Linked Incentive (PDLI)

- Up to 50% reimbursement of eligible expenditure

- Cap: ₹15 crore per application

- Deployment Linked Incentive (DLI)

- 6% → 4% of net sales turnover for 5 years

- Cap: ₹30 crore per application

- Minimum cumulative net sales (Y1–Y5):

- ₹1 crore → startups/MSMEs

- ₹5 crore → other domestic firms

- Design must be successfully deployed in products

Design-Infrastructure Support

- National EDA Tool Grid — remote access to advanced design tools

- IP Core Repository — reusable IPs for SoC design

- MPW prototyping support — shared-lot chip fabrication

- Post-silicon validation — testing & silicon bring-up support

Measured Outcomes & Data Highlights

- 24 DLI-supported chip-design projects in strategic sectors

- 16 tape-outs, 6 fabricated ASIC chips

- 10 patents filed

- 140+ reusable IP cores developed

- 1,000+ specialised engineers engaged / trained

- >3× private investment leveraged

- EDA Grid Usage: 54,03,005 hours by 95 startups

- ChipIN Centre reach:

- ~1 lakh engineers & students

- 400+ organisations

- 305 academic institutions (C2S Programme)

- 95 startups

Key Institutional Pillars

- Semicon India Programme (SIM) — investment & design ecosystem support

- Chips to Startup (C2S) — target 85,000 semiconductor-ready manpower

- Microprocessor Development Programme — indigenous VEGA, SHAKTI, AJIT families

- C-DAC, IIT-Madras, IIT-Bombay — open-source architecture leadership

Strategic Impact Pathways

- Anchors India in high-value chip-design/IP segment

- Reduces exposure to geopolitical & supply-chain shocks

- Enables assured access to technologies for defence, telecom, AI, mobility

- Drives technology autonomy + export-ready fabless capability

Representative Success Stories

- Vervesemi — motor-control ICs for appliances, drones, EVs; 110+ IPs, 10 patents

- InCore — indigenous RISC-V processor IPs; silicon-proven across 180–16 nm

- Netrasemi — India’s first indigenous AI SoC @ 12 nm for surveillance & robotics

- Aheesa Digital — VEGA-based GPON broadband SoC (Vihaan)

- AAGYAVISION — advanced radar-on-chip for safety & 6G-sensor networks

Challenges & Implementation Gaps

- Talent pipeline needs deep-specialization scaling

- Transition from prototype → volume manufacturing still evolving

- Need for stronger market linkages & downstream fabrication access

- IP commercialisation & export readiness require policy continuity

Way Forward — Policy Priorities

- Expand EDA + MPW capacity & subsidised access

- Incentivise RISC-V, edge-AI, telecom & automotive SoCs

- Strengthen design-to-manufacturing coordination with ISM fabs

- Deepen VC + industry co-funding & global partnerships

- Create national semiconductor IP marketplace and standards stack

Prelims Pointers

- Scheme type: Fabless chip-design incentive

- Ministry / Nodal: MeitY / C-DAC

- Outlay umbrella: Semicon India ₹76,000 crore

- PDLI cap: ₹15 crore | DLI cap: ₹30 crore

- Incentive band: 6% → 4% of net sales (5 years)

- Focus: ICs, SoCs, chipsets, IP cores, semiconductor-linked designs